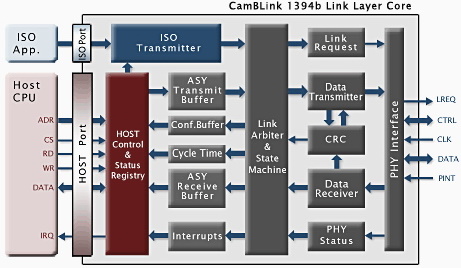

CamBLink™ IEEE1394a/b Link Layer IP Core for Digital Cameras

CamBLink™ is the easiest and fastest way to implement high-speed (up to 800 Mbps) Firewire® capability in digital cameras.

The CamBLink IP Core has been designed for the low-cost Xilinx Spartan FPGA family, but could be recompiled on request to any suitable FPGA. The design is compatible with the requirements of V1.30 of 1394 Trade Association's IIDC Digital Camera specifications.

With the small footprint (<30 kgate) CamBLink IP Core, a customized, bilingual 1394a/b Digital Camera can be designed, with maximum packet speed of 800 Mbps. A design example is provided with the license.

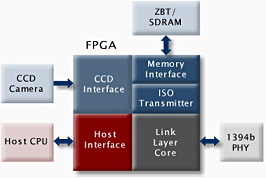

CamBLink Typical Application

GenBLink™ General Purpose IEEE1394a/b Link Layer IP Core

GenBLink is functionally similar to CamBLink, but facilitates bidirectional isochronous data exchange via IEEE1394a/b FireWire® communication. Please request additional information here.

GenBLink2™ Advanced General Purpose IEEE1394a/b Link Layer IP Core

The GenBLink2™ core is member of ATRA Vision xBlink® family of

customized embedded 1394b Link Layer Controllers. With this core, a designer can build a bilingual 1394a/1394b Node Device

with a full Isochronous Transmit, Isochronous Receive and Cycle Master Capabilities.

- Fully compliant with the IEEE standard for High-Performance Serial Bus IEEE Std 1394b™-2002

- Supports all standard 1394 Asynchronous, Isochronous and PHY packets.

- Maximum Isochronous data payload of 8KB.

- Maximum Asynchronous data payload of 4KB.

- Legacy S100-S400 1394a and Beta S100-S800 1394b Packet Transmission speed.

- 8KB Asynchronous Receive and Transmit Data Buffer implemented with Xilinx® Block Select RAM™ memory.

- Performs CRC packet header and data payload checksum/generation.

- Receives/Transmits Cycle-Start packets.

- 32bit asynchronous generic Host CPU interface with

- 32 internal Control, Status and Interrupt Registers.

- Software polling or Interrupt driven API.

- Supports data burst accesses in Big/Little Endian Modes.

- Simple ISO Receive/Transmit Data Port interfaces for custom User Application. Supports fixed/variable size byte or quadlet aligned data payload.

- Minimum size FPGA footprint for cost and power sensitive embedded applications. Optimized for low cost Xilinx® Spartan6™ FPGA family.

- Hardware design tested with:

- TSB81BA3 PHY (TI® Physical Interface Chip)

- XC5VLX30T (Virtex5™ FPGA).

- Win XP® & Win7® 1394b drivers.

Please contact us with your specific requirements, or request additional information here.

IP Core Licensing

CamBLink and GenBLink IEEE1394a/b Link Layer IP Cores can be licensed for a single project (Project License) if you only plan to implement it in a single product and its minor variations. The Project License has no time limit.

Alternately, the license can be obtained for a specified geographic location (Site License) and the IP Core can be implemented in an unlimited number of products in a 12 month period.

Both the Project and Site licences have Standard or Custom option. The difference is in the format of the file defining the core control register, for which the source code is provided for the Custom license.

Please contact us with your specific requirements, or request additional information here.

Additonal Resources

Visit the Resources section for more documentation.

|